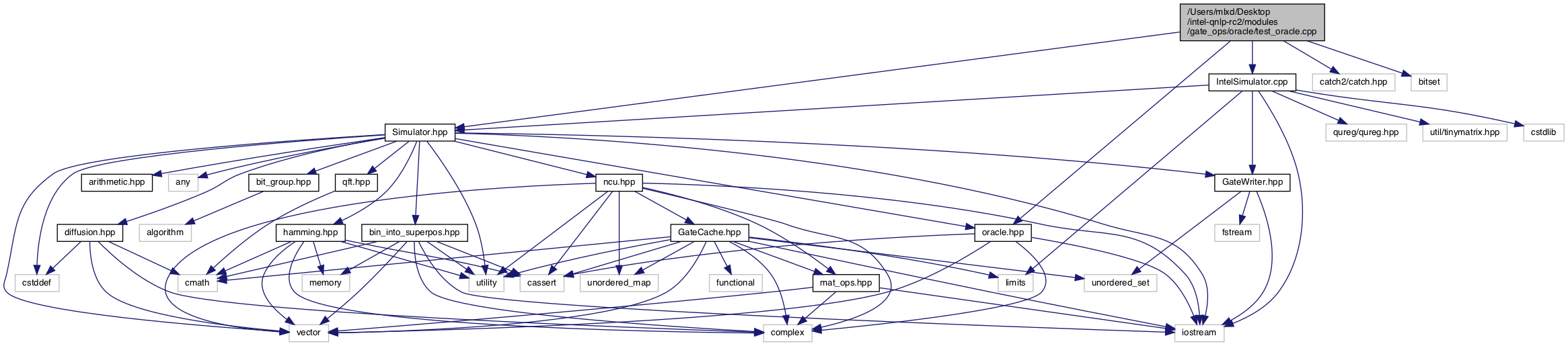

#include "oracle.hpp"#include "Simulator.hpp"#include "IntelSimulator.cpp"#include "catch2/catch.hpp"#include <bitset>

Go to the source code of this file.

Typedefs | |

| typedef ComplexDP | Type |

Functions | |

| TEST_CASE ("3 qubit Oracle standalone class","[oracle]") | |

| Test 3 qubit Oracle standalone class. More... | |

| TEST_CASE ("8 qubit Oracle standalone class","[oracle]") | |

| Test: 8 qubit Oracle standalone class. More... | |

| TEST_CASE ("3 qubit Oracle simulator method","[oracle]") | |

| Test: 3 qubit Oracle simulator method. More... | |

| TEST_CASE ("8 qubit Oracle simulator method","[oracle]") | |

| Test: 8 qubit Oracle simulator method. More... | |

Typedef Documentation

◆ Type

| typedef ComplexDP Type |

Definition at line 12 of file test_oracle.cpp.

Function Documentation

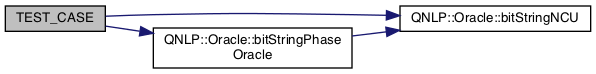

◆ TEST_CASE() [1/4]

| TEST_CASE | ( | "3 qubit Oracle standalone class" | , |

| "" | [oracle] | ||

| ) |

Test 3 qubit Oracle standalone class.

Definition at line 19 of file test_oracle.cpp.

References QNLP::Oracle< SimulatorType >::bitStringNCU(), QNLP::Oracle< SimulatorType >::bitStringPhaseOracle(), ncu_opt_tester::num_qubits, and ncu_opt_tester::sim.

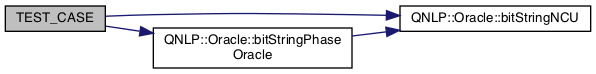

◆ TEST_CASE() [2/4]

| TEST_CASE | ( | "8 qubit Oracle standalone class" | , |

| "" | [oracle] | ||

| ) |

Test: 8 qubit Oracle standalone class.

Definition at line 118 of file test_oracle.cpp.

References QNLP::Oracle< SimulatorType >::bitStringNCU(), QNLP::Oracle< SimulatorType >::bitStringPhaseOracle(), ncu_opt_tester::num_qubits, and ncu_opt_tester::sim.

◆ TEST_CASE() [3/4]

| TEST_CASE | ( | "3 qubit Oracle simulator method" | , |

| "" | [oracle] | ||

| ) |

Test: 3 qubit Oracle simulator method.

Definition at line 220 of file test_oracle.cpp.

References ncu_opt_tester::num_qubits, and ncu_opt_tester::sim.

◆ TEST_CASE() [4/4]

| TEST_CASE | ( | "8 qubit Oracle simulator method" | , |

| "" | [oracle] | ||

| ) |

Test: 8 qubit Oracle simulator method.

Definition at line 319 of file test_oracle.cpp.

References ncu_opt_tester::num_qubits, and ncu_opt_tester::sim.