#include "ncu.hpp"#include "Simulator.hpp"#include "IntelSimulator.cpp"#include "catch2/catch.hpp"#include <bitset>

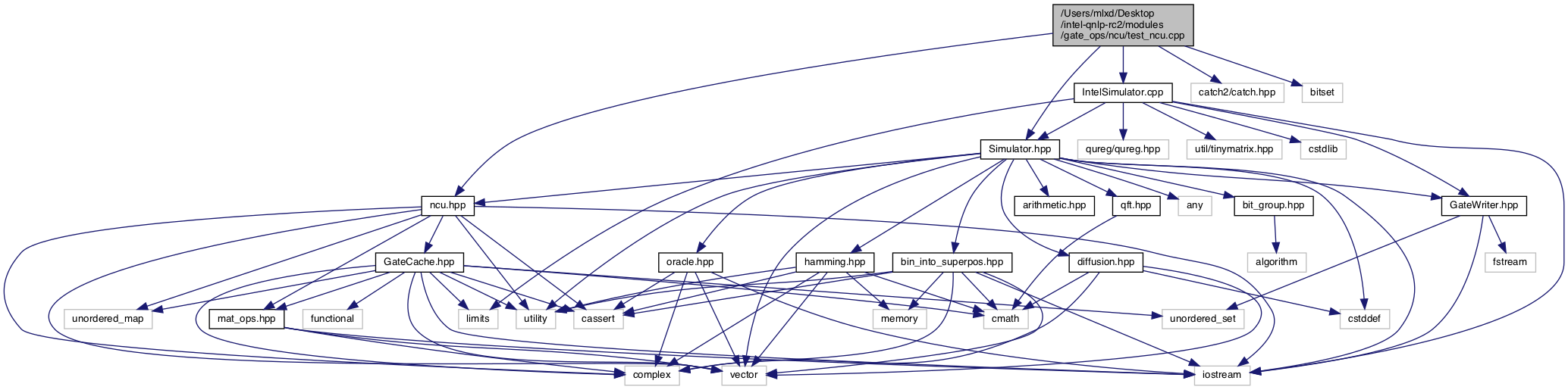

Include dependency graph for test_ncu.cpp:

Go to the source code of this file.

Typedefs | |

| typedef ComplexDP | Type |

Functions | |

| TEST_CASE ("Test n-controlled unitary module with Pauli-X |11..10>","[ncu]") | |

| Test PauliX for NCU. More... | |

| TEST_CASE ("Test n-controlled unitary module with Pauli-Z on |111..1>","[ncu]") | |

| Test Pauli-Z for NCU. More... | |

| TEST_CASE ("Test n-controlled unitary module with Pauli-X and non-adjacent controls","[ncu]") | |

| Test Pauli-X and non-adjacent controls for NCU. More... | |

Typedef Documentation

◆ Type

| typedef ComplexDP Type |

Definition at line 12 of file test_ncu.cpp.

Function Documentation

◆ TEST_CASE() [1/3]

| TEST_CASE | ( | "Test n-controlled unitary module with Pauli-X |11.. | 10, |

| " | , | ||

| "" | [ncu] | ||

| ) |

Test PauliX for NCU.

Definition at line 18 of file test_ncu.cpp.

Class definition for IntelSimulator. The purpose of this class is to map the functionality of the und...

Definition: IntelSimulator.cpp:35

References ncu_opt_tester::num_qubits, and ncu_opt_tester::sim.

◆ TEST_CASE() [2/3]

| TEST_CASE | ( | "Test n-controlled unitary module with Pauli-Z on |111.. | 1, |

| " | , | ||

| "" | [ncu] | ||

| ) |

Test Pauli-Z for NCU.

Definition at line 66 of file test_ncu.cpp.

96 // The pattern matching |11..1>|1> will flip the sign of the last qubit. Others will remain unaffected.

100 CHECK(r[pattern].imag() + 10*mach_eps == Approx(0.).margin(1e-12) ); //mach_eps to overcome floating point 0.

Class definition for IntelSimulator. The purpose of this class is to map the functionality of the und...

Definition: IntelSimulator.cpp:35

References ncu_opt_tester::num_qubits, and ncu_opt_tester::sim.

◆ TEST_CASE() [3/3]

| TEST_CASE | ( | "Test n-controlled unitary module with Pauli-X and non-adjacent controls" | , |

| "" | [ncu] | ||

| ) |

Test Pauli-X and non-adjacent controls for NCU.

Definition at line 117 of file test_ncu.cpp.

Class definition for IntelSimulator. The purpose of this class is to map the functionality of the und...

Definition: IntelSimulator.cpp:35

References ncu_opt_tester::num_qubits, and ncu_opt_tester::sim.